## DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

## COMMON FOR: DEPARTMENT OF INFORMATION TECHNOLOGY

## CS8451 – DESIGN AND ANALYSIS OF ALGORITHMS

YEAR / SEM : II / III

## **R** – 2017

## **LECTURE NOTES**

## **CS8451- DESIGN AND ANALYSIS OF ALGORITHMS**

#### UNIT I

#### SYLLABUS INTRODUCTION

Notion of an Algorithm – Fundamentals of Algorithmic Problem Solving – Important Problem Types – Fundamentals of the Analysis of Algorithmic Efficiency –Asymptotic Notations and their properties. Analysis Framework – Empirical analysis - Mathematical analysis for Recursive and Non-recursive algorithms – Visualization

## UNIT II FORCE AND DIVIDE-AND-CONQUER

Brute Force – Computing an – String Matching - Closest-Pair and Convex-Hull Problems - Exhaustive Search - Travelling Salesman Problem - Knapsack Problem - Assignment problem. Divide and Conquer Methodology – Binary Search – Merge sort – Quick sort – Heap Sort - Multiplication of Large Integers – Closest-Pair and Convex - Hull Problems.

## UNIT III DYNAMIC PROGRAMMING AND GREEDY TECHNIQUE 9

Dynamic programming – Principle of optimality - Coin changing problem, Computing a Binomial Coefficient – Floyd's algorithm – Multi stage graph - Optimal Binary Search Trees – Knapsack Problem and Memory functions. Greedy Technique – Container loading problem - Prim's algorithm and Kruskal's Algorithm – 0/1 Knapsack problem, Optimal Merge pattern - Huffman Trees.

#### UNIT IV ITERATIVE IMPROVEMENT The Simpley Method The Maximum Flow Problem Maximum Matching in Binartite Gran

The Simplex Method - The Maximum-Flow Problem – Maximum Matching in Bipartite Graphs, Stable marriage Problem.

UNIT V COPING WITH THE LIMITATIONS OF ALGORITHM POWER 9 Lower - Bound Arguments - P, NP NP- Complete and NP Hard Problems. Backtracking – n-Queen problem - Hamiltonian Circuit Problem – Subset Sum Problem. Branch and Bound – LIFO Search and FIFO search - Assignment problem – Knapsack Problem – Travelling Salesman Problem -Approximation Algorithms for NP-Hard Problems – Travelling Salesman problem – Knapsack problem.

#### **TOTAL: 45 PERIODS**

9

#### **TEXT BOOKS:**

1. Anany Levitin, —Introduction to the Design and Analysis of Algorithms ||, Third Edition, Pearson Education, 2012.

2. Ellis Horowitz, Sartaj Sahni and Sanguthevar Rajasekaran, Computer Algorithms/ C++, Second Edition, Universities Press, 2007.

#### **REFERENCES:**

1. Thomas H.Cormen, Charles E.Leiserson, Ronald L. Rivest and Clifford Stein, —Introduction to Algorithms||, Third Edition, PHI Learning Private Limited, 2012.

2. Alfred V. Aho, John E. Hopcroft and Jeffrey D. Ullman, —Data Structures and Algorithms||, Pearson Education, Reprint 2006.

3. Harsh Bhasin, —Algorithms Design and Analysis||, Oxford university press, 2016.

4. S. Sridhar, —Design and Analysis of Algorithms ||, Oxford university press, 2014.

5. http://nptel.ac.in/

#### UNIT I

#### PART A

## 1. What is an algorithm? Or Define an algorithm. (Apr\May- 2017) Or Define algorithm with its properties.(April/May 2021)

- ➤ An algorithm is a <u>finite set</u> of instructions that, if followed, accomplishes a particular task.

- > In addition, all algorithms must satisfy the following criteria:

- input

- Output

- Definiteness

- Finiteness

- Effectiveness.

## 2. Define Program.

A program is the expression of an algorithm in a programming language.

#### 3. What is performance measurement?

Performance measurement is concerned with obtaining the <u>space and the time</u> requirements of a particular algorithm.

#### 4. Write the For LOOP general format.

The general form of a for Loop is For variable : = value 1 to value 2

Step do

{

<statement 1>

<statement n >

#### 5. What is recursive algorithm?

- ✓ Recursive algorithm <u>makes more than a single</u> call to itself is known as recursive call.

- $\checkmark$  An algorithm that calls itself is Direct recursive.

- ✓ Algorithm A is said to be indeed recursive if it calls another algorithm, which in turn calls A

#### 6. What is space complexity?

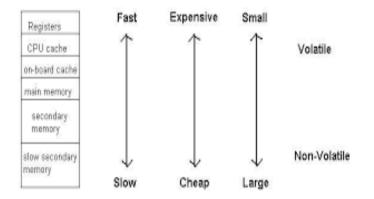

The space complexity of an algorithm is the <u>amount of memory</u> it needs to run to completion.

#### 7. What is time complexity?

The time complexity of an algorithm is the <u>amount of time</u> it needs to run to completion.

#### 8. Give the two major phases of performance evaluation.

Performance evaluation can be loosely divided into two major phases:

- > a prior estimates (performance analysis)

- > a posterior testing (performance measurement)

#### 9. Define input size.

The input size of any instance of a problem is defined to be the number of elements needed to describe that instance.

#### 10. Define best-case step count.

The best-case step count is the minimum number of steps that can be

executed for the given parameters.

#### 11. Define worst-case step count.

The worst-case step count is the maximum number of steps that can be executed for the given parameters.

#### 12. Define average step count.

The average step count is the average number of steps executed an instances with the given parameters.

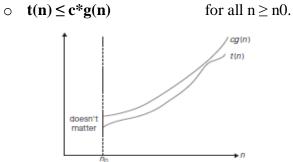

## 13. Define the asymptotic notation "Big oh" (0)

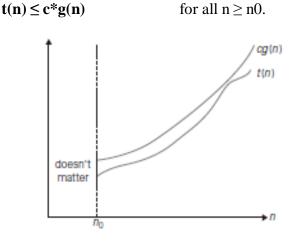

A function t(n) is said to be in O(g(n)) ( $t(n) \in O(g(n))$ ), if t(n) is bounded above by constant multiple of g(n) for all values of n, and if there exist a positive constant c and non negative integer n0 such that

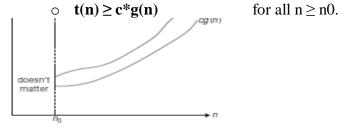

## 14. Define the asymptotic notation "Omega" ( $\Omega$ ). NOV/DEC 2021

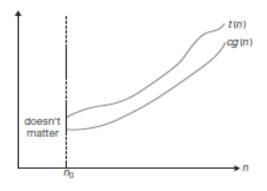

A function t(n) is said to be in  $\Omega(g(n))$  ( $t(n) \in \Omega(g(n))$ ), if t(n) is bounded below by constant multiple of g(n) for all values of n, and if there exist a positive constant c and non negative integer n0 such that  $t(n) \ge c^*g(n)$  for all  $n \ge n0$ .

Big-omega notation:  $t(n) \in \Omega(g(n))$ .

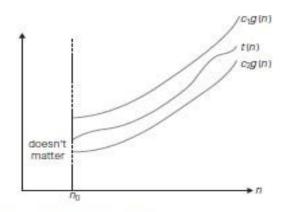

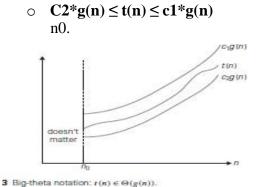

## 15. Define the asymptotic notation "theta" $(\Theta)$

A function t(n) is said to be in  $\Theta(g(n))$  ( $t(n) \in \Theta(g(n))$ ), if t(n) is bounded both above and below by constant multiple of g(n) for all values of n, and if there exist a positive constant c1 and c2 and non negative integer n0 such that  $C2^*g(n) \le t(n) \le c1^*g(n)$  for all  $n \ge n0$ .

**3** Big-theta notation:  $t(n) \in \Theta(g(n))$ .

#### 16. What is a Computer Algorithm?

An algorithm is a sequence of unambiguous instructions for solving a problem, i.e., for obtaining a required output for any legitimate input in a finite amount of time.

#### 17. What are the features of an algorithm?

More precisely, an algorithm is a method or process to solve a problem satisfying the following properties:

**Finiteness**-Terminates after a finite number of steps

Definiteness-Each step must be rigorously and unambiguously specified.

Input-Valid inputs must be clearly specified.

Output-Can be proved to produce the correct output given a valid input.

Effectiveness-Steps must be sufficiently simple and basic.

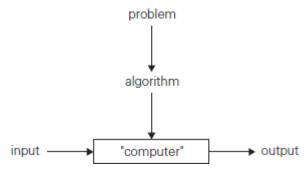

#### 18. Show the notion of an algorithm.

#### Dec 2009 / May 2013

An algorithm is a sequence of unambiguous instructions for solving a problem in a finite amount of time.

#### 19. What are different problem types?

- Sorting

- Searching

- o String Processing

- Graph problems

- Combinatorial Problems

- Geometric problems

- Numerical problems

#### 20. What are different algorithm design techniques/strategies?

- Brute force

- Divide and conquer

- Decrease and conquer

- Transform and conquer

- Space and time tradeoffs

- Greedy approach

- Dynamic programming

- Backtracking

- Branch and bound

#### 21. How to measure an algorithm's running time? Nov/Dec 2017

Unit for measuring the running time is the algorithms basic operation. The running time is measured by the count of no. of times the basic operations is executed.

**Basic operation:** the operation that contributes the most to the total running time. **Example:** the basic operation is usually the most time-consuming operation in the algorithm's innermost loop.

#### 22. How time efficiency is analyzed?

Let  $c_{op}$  – execution time of algorithms basic operation on a particular computer.

c(n) – no. of times this operation need to be executed.

T(n) – running time.

Running time is calculated using the formula

$$\mathbf{T}(\mathbf{n}) \approx \mathbf{c}_{\mathrm{op}} \, \mathbf{c}(\mathbf{n})$$

#### 23. What are orders of growth?

Orders of Growth

| n        | $\log_2 n$ | n        | $n \log_2 n$       | $n^2$     | $n^3$     | $2^n$               | n!                   |

|----------|------------|----------|--------------------|-----------|-----------|---------------------|----------------------|

| 10       | 3.3        | 101      | $3.3 \cdot 10^{1}$ | $10^{2}$  | $10^{3}$  | $10^{3}$            | $3.6 \cdot 10^{6}$   |

| $10^{2}$ | 6.6        | $10^{2}$ | $6.6 \cdot 10^{2}$ | $10^{4}$  | $10^{6}$  | $1.3 \cdot 10^{30}$ | $9.3 \cdot 10^{157}$ |

| $10^{3}$ | 10         | $10^{3}$ | $1.0 \cdot 10^4$   | $10^{6}$  | $10^{9}$  |                     |                      |

| $10^{4}$ | 13         | $10^{4}$ | $1.3 \cdot 10^{5}$ | $10^{8}$  | $10^{12}$ |                     |                      |

| $10^{5}$ | 17         | $10^{5}$ | $1.7 \cdot 10^{6}$ | 1010      | $10^{15}$ |                     |                      |

| $10^{6}$ | 20         | $10^{6}$ | $2.0 \cdot 10^{7}$ | $10^{12}$ | $10^{18}$ |                     |                      |

## 24. What are basic efficiency classes?

Basic Efficiency classes

| 1          | Constant     |

|------------|--------------|

| log n      | Logarithmic  |

| п          | Linear       |

| $n \log n$ | Linearithmic |

| $n^2$      | Quadratic    |

| $n^3$      | Cubic        |

| $2^n$      | Exponential  |

| n!         | Factorial    |

#### 25. Give an example for basic operations.

Input size and basic operation examples

| Problem                     | Input size measure         | Basic operation       |  |  |

|-----------------------------|----------------------------|-----------------------|--|--|

| Searching for key in a list | Number of list's items,    | Key comparison        |  |  |

| of <i>n</i> items           | i.e. <i>n</i>              |                       |  |  |

| Multiplication of two       | Matrix dimensions or total | Multiplication of two |  |  |

| matrices                    | number of elements         | numbers               |  |  |

| Checking primality of a given integer <i>n</i> | size = number of digits<br>(in binary representation) | Division                                |

|------------------------------------------------|-------------------------------------------------------|-----------------------------------------|

| Typical graph problem                          | Number of vertices and/or edges                       | Visiting a vertex or traversing an edge |

## 26. What are six steps processes in algorithmic problem solving? Dec 2009

- 1. Understanding the problem.

- 2. Ascertaining the capabilities of a computational device.

- 3. Choosing between exact and approximate problem solving.

- 4. Deciding on appropriate data structures.

- 5. Algorithm Design Techniques.

- 6. Methods of specifying an algorithm

- 7. Proving an algorithm's correctness.

- 8. Analysing an algorithm.

- 9. Coding an algorithm.

## 27. What do you mean by Amortized Analysis?

- ✓ Amortized analysis finds the average running time per operation over a worst case sequence of operations.

- ✓ Amortized analysis differs from average-case performance in that probability is not involved; amortized analysis guarantees the time per operation over worst-case performance.

## 28. Define order of an algorithm.

Measuring the performance of an algorithm in relation with the input size n is known as order of growth.

## 29. How is the efficiency of the algorithm defined? Or . How do you measure the efficiency of an algorithm? May/June 2019

The efficiency of an algorithm is defined with the components.

- (i) Time efficiency -indicates how fast the algorithm runs

- (ii) Space efficiency -indicates how much extra memory the algorithm needs

#### 30. What are the characteristics of an algorithm?

Every algorithm should have the following five characteristics

- (i) Input

- (ii) Output

- (iii) Definiteness

- (iv) Effectiveness

- (v) Termination

## 31. What are the different criteria used to improve the effectiveness of algorithm?

(i) The effectiveness of algorithm is improved, when the design, satisfies the following constraints to be minimum.

Time efficiency - how fast an algorithm in question runs.

Space efficiency – an extra space the algorithm requires.

(ii) The algorithm has to provide result for all valid inputs.

## 32. Analyse the time complexity of the following segment:

for(i=0;i<N;i++) for(j=N/2;j>0;j--) sum++:

Time Complexity= N \* N/2 = N<sup>2</sup> /2  $\in$  O(N<sup>2</sup>)

## 33. Write general plan for analysing non-recursive algorithms.

i. Decide on parameter indicating an input's size.

ii. Identify the algorithm's basic operation

iii. Check the no. of times basic operation executed depends on size of input. if it depends on some additional property, then best, worst, average cases need to be investigated

iv. Set up sum expressing the no. of times the basic operation is executed. (establishing order of growth)

## 34. How will you measure input size of algorithms?

The time taken by an algorithm grows with the size of the input. So the running time of the program depends on the size of its input. The input size is measured as the number of items in the input that is a parameter n is indicating the algorithm's input size.

#### 35. Write general plan for analysing recursive algorithms.

i. Decide on parameter indicating an input's size.

- ii. Identify the algorithm's basic operation

- iii. Checking the no. of times basic operation executed depends on size of input. if it depends on some additional property, then best, worst, average cases need to be investigated

- iv. Set up the recurrence relation, with an appropriate initial condition, for the number of times the basic operation is executed

v. Solve recurrence (establishing order of growth)

## 36. What do you mean by Combinatorial Problem?

Combinatorial Problems are problems that ask to find a combinatorial object-such as permutation, a combination, or a subset-that satisfies certain constraints and has some desired properties.

#### 37. Define Little "oh".

The function f(n) = O(g(n)) if and only if

$n \rightarrow \infty$

$$Lim \quad f(n) / g(n) = 0$$

The function

$$f(n) = \omega(g(n))$$

)) if and only if

$$\lim_{n \to \infty} f(n) / g(n) = 0$$

$$\rightarrow \infty$$

**39.** Write algorithm using iterative function to fine sum of n numbers.

Algorithm

sum(a, n)

$$\begin{cases}

S := 0.0 \\

For i=1 to n \\

do \\

S : - S + a[i] \\

Return S;

\end{cases}$$

40. Write an algorithm using Recursive function to fine sum of n numbers.

Algorithm

{

Rsum (a, n)

{

If(

$$n \le 0$$

) then

Return 0.0;

Else

Return Rsum(a, n- 1) + a(n);

41. Describe the recurrence relation for merge sort?

If the time for the merging operation is proportional to n, then the computing time of merge described by the recurrence relation sort is T(n) =n = 1, a a constant a 2T(n/2) + nn >1, c a constant *Dec 2012* Part A – Refer Q. No. 6 & 7 42. What is time and space complexity? 43. Define Algorithm validation. Dec 2012 The process of measuring the effectiveness of an algorithm before it is coded to know whether the algorithm is correct for every possible input. This process is called validation. 44. Differentiate time complexity from space complexity. May 2010 Part A – Refer Q. No. 6 & 7 45. What is a recurrence equation? *May 2010* A recurrence [relation] is an equation or inequality that describes a function in terms of its values on smaller inputs. Examples: Factorial: multiply n by (n-1)!T(n) = T(n-1) + O(1) -> O(n)Fibonacci: add fibonacci(n - 1) and fibonacci(n - 2) $T(n) = T(n-1) + T(n-2) \rightarrow O(2^n)$ 46. What do you mean by algorithm? May 2013 Part A – Refer Q. No. 1, 16 & 18 47. Define Big Oh Notation. May 2013 Part A - Refer Q. No. 13 48. What is average case analysis? May 2014 The average case analysis of an algorithm is analysing the algorithm for the average input of size n, for which the algorithm runs at an average between the longest and the fastest time. 49. Define program proving and program verification. May 2014  $\checkmark$  Given a program and a formal specification, use formal proof techniques (e.g. induction) to prove that the program behaviour fits the specification.  $\checkmark$  Testing to determine whether a program works as specified. 50. Define asymptotic notation. *May 2014* Asymptotic notations are mathematical tools to represent time complexity of algorithms for measuring their efficiency. Types : Big Oh notation - 'O' Omega notation - ' $\Omega$ ' Theta notation - ' $\Theta$ ' Little Oh notation - 'o ' Little Omega notation - ' $\Omega$ ' 51. What do you mean by recursive algorithm? May 2014 Part A – Refer Q. No. 5 52. Establish the relation between O and  $\Omega$ Dec 2010  $f(n) \in \Omega(g(n)) \Leftrightarrow g(n) \in O(f(n))$ **Proof:**  $O(f(n)) = \{g: N \rightarrow N \mid \exists c, n \in N \forall n \ge n : g(n) \le c \cdot f(n)\}$  $\Omega(g(n)) = \{f: N \rightarrow N \mid \exists c, n \in N \forall n \ge n : f(n) \ge c \cdot g(n) \}$ **Step 1/2:**  $f(n) \in \Omega(g(n)) \Leftrightarrow g(n) \in O(f(n))$ 9

$\begin{array}{l} \exists c, n 0 \in \mathbb{N} \ \forall n \geq n 0: \ f(n) \geq c \cdot g(n) \Rightarrow f(n)g(n) \geq c \Rightarrow 1g(n) \geq cf(n) \Rightarrow g(n) \leq 1c \cdot f(n) \\ & \text{And this is exactly the definition of } O(f(n)). \\ \textbf{Step 2/2: } f(n) \in \Omega(g(n)) \leftarrow g(n) \in O(f(n)) \\ & \exists c, n 0 \in \mathbb{N} \ \forall n \geq n 0: \ g(n) \leq c \cdot f(n) \Rightarrow ... \Rightarrow f(n) \geq 1c \cdot g(n) \\ & \text{Hence proved.} \end{array}$

#### 53. If $f(n) = a_m n^m + ... + a_1 n + a_0$ . Prove that $f(n)=O(n^m)$ . Dec 2010 Refer Class note.

#### 54. What is best case analysis? Or Best case efficiency.

The best case analysis of an algorithm is analysing the algorithm for the best case input of size n, for which the algorithm runs the fastest among all the possible inputs of that size.

#### 55. what do you mean worst case efficiency of algorithm.Nov/Dec 2017

The worst case analysis of an algorithm is analysing the algorithm for the worst case input of size n, for which the algorithm runs the longest among all the possible inputs of that size.

## 56. Consider an algorithm that finds the number of binary digits in the binary representation of a positive decimal integer. (AU april/may 2015)

Number of major comparisons= $|\log 2n| + 1 \in \log 2n$ .

Algorithm 3: Finding the number of binary digits in the binary representation of a positive decimal integer.

```

Algorithm Binary(n)

count:=1;

whilen >1

do

count:=count+ 1;

n:=[n/2];

end

return count;

```

#### 57. write down the properties of asymptotic notations.(AU april/may 2015)

The following property is useful in analyzing algorithms that comprise two consecutively executed parts.

#### Theorem

If  $t_1(n) = O(g_1(n))$  and  $t_2(n) \in O(g_2(n))$  then,  $t_1(n) + t_2(n) \in (\max \{g_1(n), g_2(n)\})$

#### Proof

Since  $t_1(n) \in O(g_1(n))$ , there exist some constant  $C_1$  and some non negative integer  $n_1$  such that

$t_1(n) \leq C_1 (g_1(n))$  for all  $n \geq n_1$

Since

$\begin{array}{l} t_2(n) & O(g_2(n)) \\ t_2(n) \leq C_2 \ (g_2(n)) \ \text{for all } n \geq n_2 \end{array}$

Let us denote,

$C_3 = \max \{C_1, C_2\}$  and

Consider  $n \ge max \{n_1, n_2\}$ , so that both the inequalities can be used.

The addition of two inequalities becomes,

$\begin{array}{l} t_1(n) + t_2(n) &\leq C_1 \; (g_1(n)) + C_2 \; (g_2(n)) \\ &\leq C_3 \; (g_1(n)) + C_3 \; (g_2(n)) \\ &\leq C_3 \; 2 \; \max\{g_1(n), \; (g_2(n))\} \end{array}$

Hence,

$t_1(n) + t_2(n) \in O(\max \{g_1(n), g_2(n)\}),$

with the constants C and  $n_0$  required by the definition being  $2C_3 = 2 \max (C_1, C_2)$  and  $\max \{n_1, n_2\}$  respectively.

The property implies that the algorithms overall efficiency will be determined by the part with a larger order of growth.

(i.e.) its least efficient part is

$\begin{array}{ll} t_1(n) \in O(g_1(n)) & t_1(n) + t_2(n) \in O \ (max \ \{g_1(n), g_2(n)\}) \\ t_2(n) \in O(g_2(n)) & \end{array}$

58. Give the Euclid's algorithm for computing gcd(m, n) (AU nov 2016) or write an algorithm to compute the greatest common divisor of two numbers (Apr/ May-2017)(or) Give the Euclid's algorithm for computing gcd of two numbers. (May/June 2018)

|                 | 2         |           |

|-----------------|-----------|-----------|

| Polynomial      | Quadratic | Quadratic |

| 1               | 0         | 1         |

| 2               | 1         | 4         |

| 4               | 6         | 16        |

| 8               | 28        | 64        |

| 10              | 45        | $10^{2}$  |

| 10 <sup>2</sup> | 4950      | 104       |

| Complexity      | Low       | High      |

| Growth          | Low       | high      |

**ALGORITHM** *Euclid\_gcd(m, n)*

//Computes gcd(m, n) by Euclid's algorithm //Input: Two nonnegative, not-both-zero integers *m* and *n* //Output: Greatest common divisor of *m* and *n* while  $n \neq 0$  do  $r \leftarrow m \mod n$  $m \leftarrow n$

$m \leftarrow n$  $n \leftarrow r$ **return** m

Example: gcd(60, 24) = gcd(24, 12) = gcd(12, 0) = 12. 59. Compare the order of growth n(n-1)/2 and  $n^2$ . (AU nov 2016)

n(n-1)/2 is lesser than the half of  $n^2$

60. The (*log n*)th smallest number of n unsorted numbers can be determined in O(n) averagecase time

Ans: True

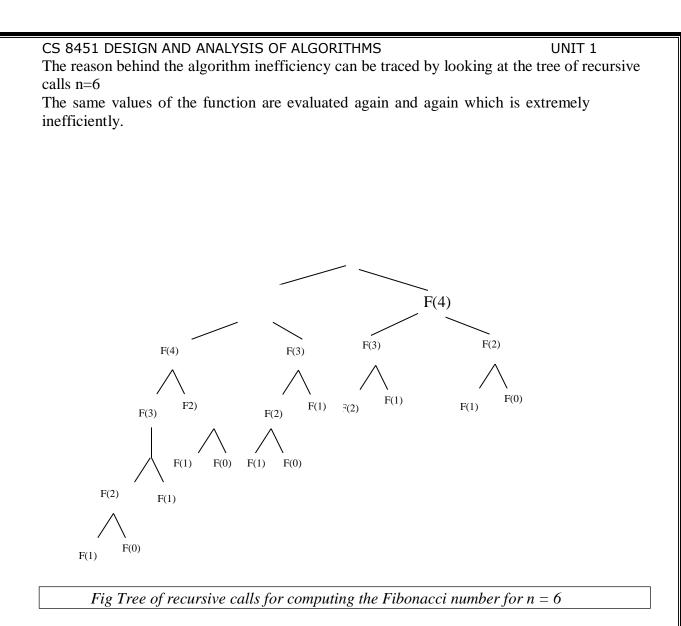

61. Fibonacci algorithm and its recurrence relation Algorithm for computing Fibonacci numbers

#### First method

## Algorithm F(n) //Computes the nth Fibonacci number recursively by using its definition. //Input: A nonnegative integer n //Output: The nth Fibonacci number if n<1 return n Else

return F(n-1)+(n-2)

the algorithm's basic operation is addition.

Let A(n) is the number of additions performed by the algorithm to compute F(n).

The number of additions needed to compute F(n-1) is A(n-1) and the number of additions needed to compute F(n-2) is A(n-2).

#### 62. Design an algorithm to compute the area and circumference of a circle

1. Find Area, Diameter and Circumference of a Circle.

#### ALGORITHM

Step 1: Start

Step 2: Initialize PI to 0

Step 3: Read radius of the circle

Step 4: Calculate the product of radius with itself and PI value

Step 5: Store the result in variable area

Step 6: Calculate the product of radius with 2

Step 7: Store the result in variable diameter

Step 8: Calculate the product of PI and diameter value

Step 9: Store the result in variable circumference

Step 10: Print the value of area, diameter and circumference

Step 11: Stop

#### PSEUDO CODE

```

Step 1: Begin

Step 2: Set PI to 3.14

Step 3: Read radius

Step 4: Compute the product of radius with itself and PI value

Step 5: Set the result to area

Step 6: Compute the product of radius with 2

Step 7: Set the result to diameter

Step 8: Calculate the product of PI and diameter value

Step 9: Set the result to circumference

Step 10: Display area, diameter, circumference

Step 11: Fnd

```

#### 63. What is a basic operation?

A basic operation could be: An assignment. A comparison between two variables. An arithmetic operation between two variables. The worst-case input is that input assignment for which the most basic operations are performed.

Basic Operations on Sets. The set is the basic structure underlying all of mathematics. In algorithm design, sets are used as the basis of many important abstract data types, and many techniques have been developed for implementing set-based abstract data types.

#### 64. Define algorithm. List the desirable properties of an algorithm.

Algorithm is a step-by-step procedure, which defines a set of instructions to be executed in a certain order to get the desired output. Algorithms are generally created independent of underlying languages, i.e. an algorithm can be implemented in more than one programming language.

An algorithm must satisfy the following properties: Input: The algorithm must have input values from a specified set. The output values are the solution to a problem. Finiteness: For any input, the algorithm must terminate after a finite number of steps. Definiteness: All steps of the algorithm must be precisely defined.

#### 65. Define best, worst, average case time complexity.

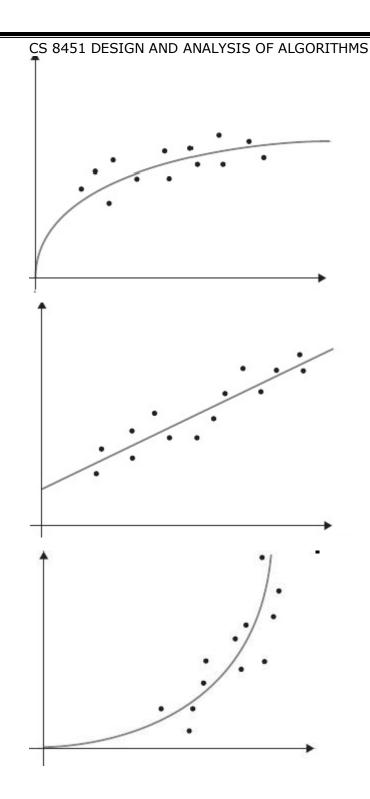

- The *worst-case complexity* of the algorithm is the function defined by the maximum number of steps taken on any instance of size *n*. It represents the curve passing through the highest point of each column.

- The *best-case complexity* of the algorithm is the function defined by the minimum number of steps taken on any instance of size *n*. It represents the curve passing through the lowest point of each column.

- Finally, the *average-case complexity* of the algorithm is the function defined by the average number of steps taken on any instance of size *n*.

#### 66. Prove that the of f(n)=o(g(n)) and g(n)=o(f(n)), then $f(n)=\theta g(n)$ . OR state the transpose symmetry property of O and $\Omega$ April/May 2019, Nov/Dec 2019

**Given function**:

$\begin{array}{ll} f(n) \mbox{ and } g(n) \\ f(n) = O(g(n)) \mbox{ when } f(n) \leq C_1 g(n) & \mbox{ for all } n \geq n_0 \hdots n_0 \hdots n_1 \hdots n_1 \hdots n_2 \hdots n_1 \hdots n_2 \hdots n_2 \hdots n_2 \hdots n_2 \hdots n_1 \hdots n_2 \hdot$

#### 67. Define recursion

A function may be recursively defined in terms of itself. A familiar example is the Fibonacci number sequence: F(n) = F(n - 1) + F(n - 2).

For such a definition to be useful, it must be reducible to non-recursively defined values: in this case F(0) = 0 and F(1) = 1. ccurs when a thing is defined in terms of itself or of its type. Recursion is used in a variety of disciplines ranging from linguistics to logic.

The most common application of recursion is in mathematics and computer science, where a function being defined is applied within its own definition.

While this apparently defines an infinite number of instances (function values), it is often done in such a way that no loop or infinite chain of references can occur.

#### 68. List the reasons for choosing an approximate algorithm.

Approximation algorithms are typically used **when finding an optimal solution is intractable**, but can also be used in some situations where a near-optimal solution can be found quickly and an exact solution is not needed. Many problems that are NP-hard are also non-approximable assuming P≠NP. <u> PART – B</u>

May2014

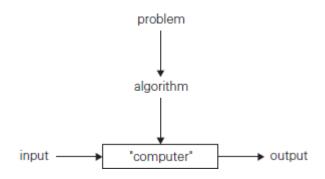

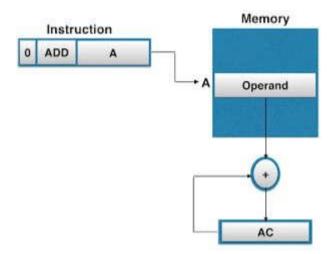

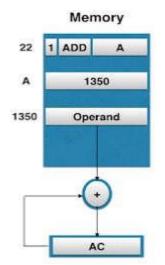

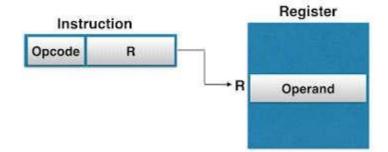

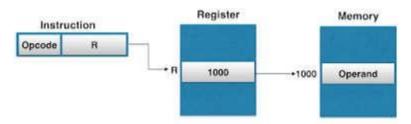

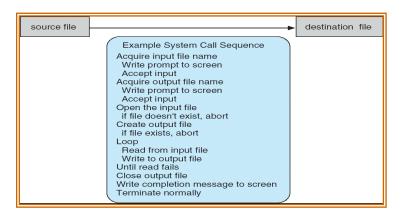

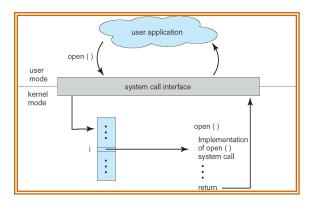

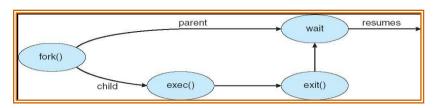

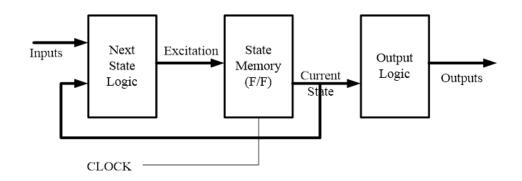

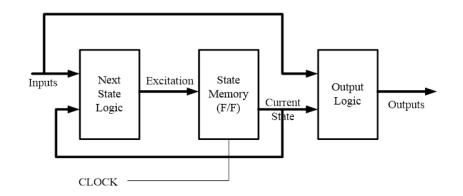

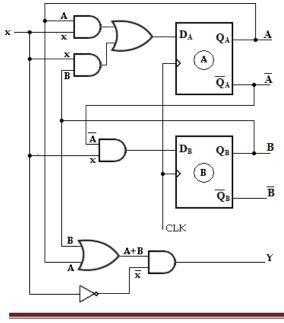

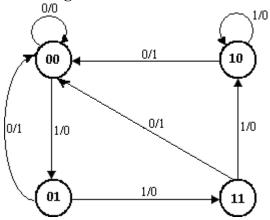

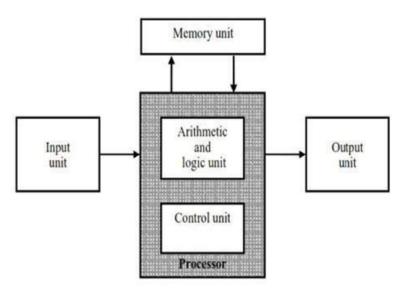

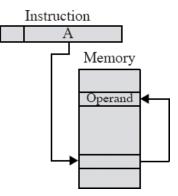

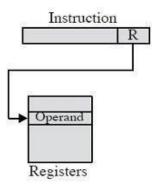

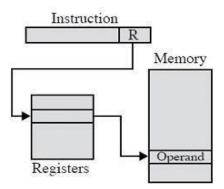

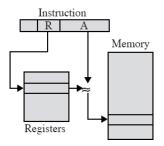

- *1*. Explain the notion of an algorithm with diagram. Synopsis:

- > Introduction

- Definition

- Diagram

- Characteristics of an Algorithm / Features of an Algorithm

- Rules for writing an Algorithm

- Implementation of an Algorithm

- > Order of an Algorithm

- > Program

- ► Example : GCD

## Introduction:

- An algorithm is a sequence of finite number of steps involved to solve a particular problem.

- An input to an algorithm specifies an instance of the problem the algorithm solves.

- An algorithm can be specified in a natural language or in a pseudo code.

- Algorithm can be implemented as computer programs.

- The same algorithm can be represented in several different ways.

- Several algorithms for solving the same problem may exist.

- Algorithms for the same problem can be based on different ideas and can solve the problem with dramatically different speeds.

## **Definition**:

- An algorithm is a sequence of non ambiguous instructions for solving a problem in a finite amount of time.

- Each algorithm is a module, designed to handle specific problem.

- The non ambiguity requirement for each step of an algorithm cannot be compromised.

- The range of inputs for which an algorithm works has to be specified carefully.

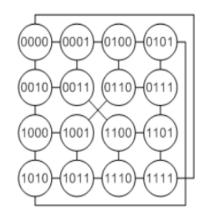

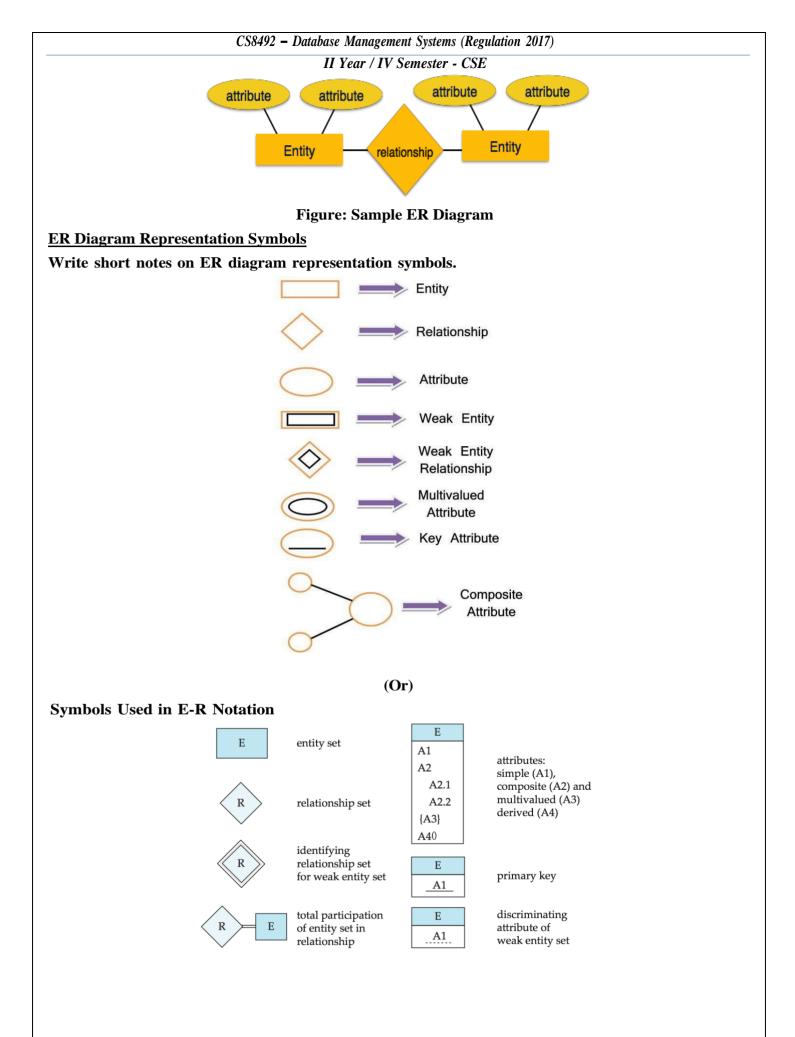

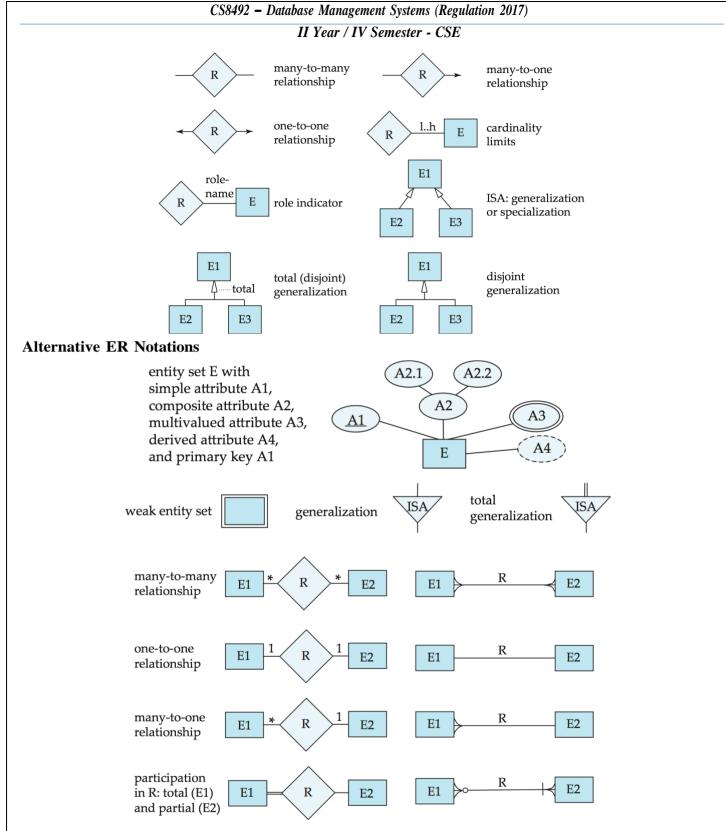

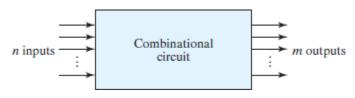

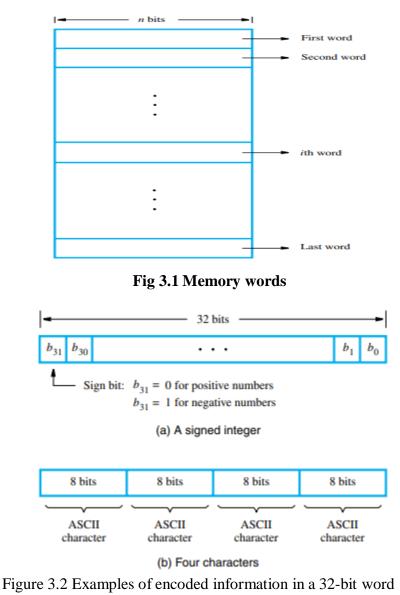

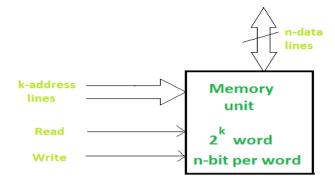

## **Diagram:**

## Characteristics of an algorithm / Features of an Algorithm

- The important and prime characteristics of an algorithm are,

- ✓ **Input**:Zero or more quantities are externally supplied.

- ✓ **Output:**At least one quantity is produced.

- ✓ **Definiteness:**Each instruction is clear and unambiguous.

- ✓ **Finiteness:**For all cases the algorithm terminates after a finite number of steps.

- ✓ **Efficiency:**Every instruction must be very basic.

- ✓ An algorithm must be expressed in a fashion that is completely free of ambiguity.

- ✓ It should be efficient.

- ✓ Algorithms should be concise and compact to facilitate verification of their correctness.

## Writing an algorithm

• Algorithm is basically a sequence of instructions written in simple English language.

• The algorithm is broadly divided into two sections

## Algorithm heading

It consists of name of algorithm, problem description , input

and output.

## **Algorithm Body**

It consists of logical body of the algorithm by making use of

various programming constructs and assignment statement.

## Rules for writing an algorithm.

Algorithm is a product consisting of heading and body. The heading consists of keyword **algorithm** and name of the algorithm and parameter list. The syntax is

## Algorithm name ( p1, p2,..... pn )

1. Then in the heading section we should write following things :

## // Problem Description;

// Input:

## //Output:

- 2. Then body of an algorithm is written, in which various programming constructs like if , for , while or some assignment statement may be written.

- 3. The compound statements should be enclosed within { and } brackets.

- 4. Single line comments are written using // as beginning of comment.

- 5. The **identifier** should begin by latter and not by digit. An identifier can be a combination of alphanumeric string.

- It is not necessary to write data types explicitly for identifiers. It will be represented by the context itself.

- Basic data types used are integer, float, and char, Boolean and so on.

- The pointer type is also used to point memory locations.

- The compound data type such as structure or record can also be used.

- 6. Using assignment operator  $\leftarrow$  an assignment statement can be given.

#### For instance: **Variable** $\leftarrow$ **expression**

- There are other types of operators' such as Boolean operators such as true or false. Logical operators such as AND, OR, NOT. And relational operators such as < , <= , >, >=, = , !=.

- 8. The array indices are stored with in square brackets '[' ']'. The index of array usually starts at zero. The multidimensional arrays can also be used in algorithm.

- 9. The inputting and outputting can be done using read and write.

For example:

#### Write ("this message will be displayed on console "); Read (Val);

10. The conditional statements such as if -then - else are written in following form

If (condition) then statement

If (condition) then statement else statement

If the if - then statement is of compound type then {and} should be used for enclosing block

11. While statement can be written as :

While (condition)do

{

Statement 1 Statement 2

## Statement n

While the condition is true the block enclosed with { } gets executed otherwise statement after} will be executed.

12. The general form for writing for loop is :

```

For variable \leftarrow value<sub>1</sub> to value<sub>n</sub> do

```

```

Statement 1

Statement 2

:

Statement n

```

Here value<sub>1</sub> is initialization condition and value<sub>n</sub> is a terminating condition the step indicates the increments or decrements in value<sub>1</sub> for executing the for loop. Sometime a keyword step is used to denote increment or decrement the value of variable for example

For  $i \leftarrow 1$  to n step 1 { Write (i)

}

Here variable i is incremented by 1 at each iteration

13. The repeat – until statement can be written as

```

Repeat

```

```

Statement 1

Statement 2

:

Statement n

```

```

Until (condition)

```

14. The break statement is used to exit from inner loop. The return statement is used to return control from one point to another. Generally used while exiting from function Note: The statements in an algorithm executes in sequential order i.e. in the same order as they appear – one after the other

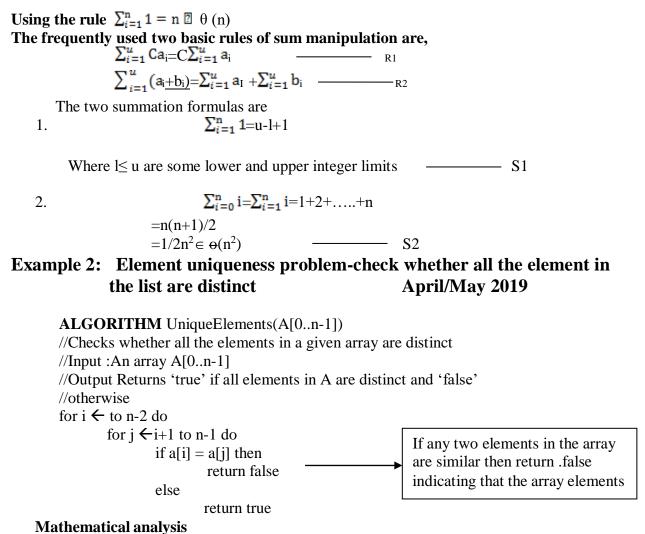

Example 1 : Write an algorithm to count the sum of n numbers

```

Algorithm sum (1, n)

```

//Problem description : this algorithm is for finding the //sum of given n numbers //Input: 1 to n numbers //Output: the sum of n numbers Result  $\leftarrow 0$ For i 1 to n do  $i \leftarrow i+1$ Result  $\leftarrow$  result + i Return result

Example 2: Write an algorithm to check whether given number is even or odd.

Algorithm eventest (val) //Problem description : this algorithm test whether given //number is even or odd //Input: the number to be tested i.e .val //Output: appropriate messages indicating even or odd

```

If (val % 2 = 0) then

Write ("given number is even ")

Else

Write ("given number is odd")

```

**Example 3**: Write an algorithm for sorting the elements.

Algorithm sort (a, n) //Problem description: sorting the elements in ascending //order //Input: an array in which the elements in ascending order //is total number of elements in the array //Output: the sorted array For i 1 to n do For j i + 1 to n-1 do If (a[i]>a[j]) then { temp  $\leftarrow$  a[i] a[i]  $\leftarrow$ a[j] a[j]  $\leftarrow$ temp }

Write ("list is sorted")

**Example 4**: Write an algorithm to find factorial of n number.

#### Algorithm fact (n)

Return n \* fact(n-1)

#### Example 5:

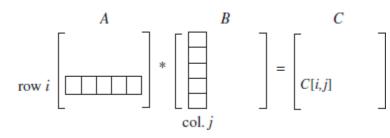

Write an algorithm to perform multiplication of two matrices

**Algorithm** mul (A, b, n)

//Problem description: this algorithm is for computing //multiplication of two matrices //Input : the two matrices A, B and order of them as n //Output : The multiplication result will be in matrix c For  $i \leftarrow 1$  to n do

> For  $j \leftarrow 1$  to n do C  $[i,j] \leftarrow 0$

For  $k \leftarrow 1$  to n do C[I,j]  $\leftarrow$ c[i,j] +A[i,k]B[k,j]

#### **Implementation of algorithms**

An algorithm describes what the program is going to perform. It states some of the actions to be executed and the order in which these actions are to be executed.

The various steps in developing algorithm are,

- 1. Finding a method for solving a problem. Every step of an algorithm should be in a precise and in a clear manner. Pseudo code is also used to describe the algorithm.

- 2. The next step is to validate the algorithm. This step includes, all the algorithm should be done manually by giving the required input, performs the required steps including in the algorithm and should get the required amount of output in an finite amount of time.

- 3. Finally, implement the algorithm in terms of programming language.

#### Order of an algorithm

The order of an algorithm is a standard notation of an algorithm that has been developed to represent function that bound the computing time for algorithms. It is an order notation. It is usually referred as O-notation.

## Example

Problem size = 'n' Algorithm = 'a' for problem size n The document mechanism execution =  $Cn^2$  times where C - constant Then the order of the algorithm 'a' =  $O(n^2)$ where  $n^2$  = Complexity of the algorithm 'a'.

## Program

- A set of explicit and unambiguous instructions expressed using a programming languages constructs is called a program.

- An algorithm can be converted into a program, using any programming language. Pascal, Fortran, COBOL, C and C++ are some of the programming languages.

#### Difference between program and algorithm:

| Sno | Algorithm                                                            | Program                                                     |  |  |  |

|-----|----------------------------------------------------------------------|-------------------------------------------------------------|--|--|--|

| 1   | Algorithm is finite.                                                 | Program need to be finite.                                  |  |  |  |

| 2   | Algorithm is written using natural language or algorithmic language. | Programs are written using a specific programming language. |  |  |  |

## 1.A. write an algorithm using recursion that determines the GCD of two numbers.Determine the time and space complexity Nov/Dec 2019

#### **Example : Calculating Greatest common Divisor**

The Greatest common Divisor (GCD) of two non zero numbers a and b is basically the largest integer that divides both a and b evenly i.e with a remainder of zero. GCD using three methods

- 1. Euclid's algorithm

- 2. Consecutive integer checking algorithm

- 3. Finding Gusing repetitive factors

## Euclid's algorithm to compute Greatest Common Divisor (GCD) of two non negative integers.

Euclid's algorithm is based on applying related equality

gcd (m, n) = gcd (n, m mod n) until the m and n is equal to 0

Where m mod n is the remainder of the division of m by n

Step 1: Start

Step 2: If n = 0, return the value of m as the answer and stop, otherwise proceed to step 3.

Step 3: Divide m by n and assign the value of the remainder to r. Step 4: Assign the value of n to m and the value of r to n. Goto step 2 Step 5: Stop

#### ALGORITHM Euclid(m, n)

//Computes gcd(m, n) by Euclid's algorithm //Input: Two nonnegative, not-both-zero integers m and n //Output: Greatest common divisor of m and n while  $n \neq 0$  do  $r \leftarrow m \mod n$

$m \leftarrow n$

$n \leftarrow r$

return m

Example, gcd (60,24) can be computed as follows,

gcd (60,24)

gcd (m, n) m =60, n=24; m/n = 2 (remainder 12) n=m=24 r=n=12 m/2 = 2 (remainder 0) n=m=12 r=n=0

gcd (12, 0) =12

gcd (24, 12)

Hence, gcd(60, 24) = gcd(24, 12) = gcd(12, 0) = 12

#### 2. Consecutive integer checking algorithm

In this method while finding the GCD of a and b we first of all find the minimum value of them. Suppose if , value of b is minimum then we start checking the divisibility by each integer which is lesser than or equal to b.

Example:

a = 15 and b =10 then t = min(15,10) since 10 is minimum we will set value of t = 10 initially. **Consecutive integer checking algorithm for computing gcd(m, n)**

Step 1: Start

Step 2: Assign the value of mini {m, n} to t

Step 3: Divide m by t. If the remainder of this division is 0, go to step 4, Otherwise go o step 5.

Step 4: Divide n by t. If the remainder of this division is 0, return the value of t as the answer and stop. Otherwise proceed to step 5.

Step 5: Decrease the value of t by I. Go to step 3.

Step 6: Stop

**Algorithm** GCD intcheck (a,b)

//Problem description : this algorithm computes the GCD of //two

numbers a and b using consecutive integer checking

//method

//Input : two integers a and b

//Output: GCD value of a and b

t ← min ( a, b)

while (t>=1) do

{

If ( a mod t == 0 AND b mod t == 0) then

Return t

Else  $t \leftarrow t-1$ Return 1

}

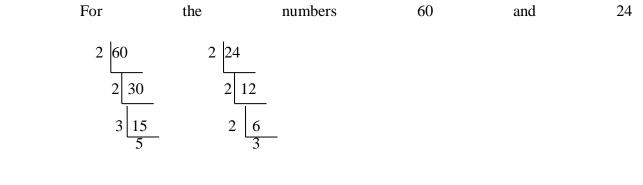

#### **3. Finding GCD using repetitive factors**

The third procedure for finding the greatest common divisor is middle school procedure.

#### Middle School Method

$$60 = \underline{2x2x3} \times 5$$

$$24 = \underline{2x2x3} \times 2$$

gcd (60,24) =  $\underline{2x2x3} = 12$

#### Algorithm:

Step 1: Start

Step 2: Find the prime Factor of m.

Step 3: Find the prime factors of n.

Step 4: Identify all the common factors in the two prime expressions Found in step 2 and step 3. If P is a common factor occurring pm and pn times in m and n respectively. It should be repeated min (pm, and pn) times.

Step 5: Compute the product of the all the common factors and return it as the greatest common divisor of the numbers given.

Step 6: Stop.

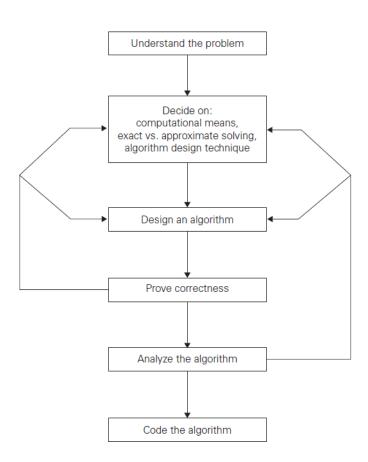

#### 2. Explain the Fundamentals of Algorithmic problem solving. Or explain the steps involved in problem solving May 2014 ,April/May 2019

Sequential steps in designing and analysing an algorithm

- 1. Understanding the problem.

- 2. Ascertaining the capabilities of a computational device.

- 3. Choosing between exact and approximate problem solving.

- 4. Deciding on appropriate data structures.

- 5. Algorithm Design Techniques.

- 6. Methods of specifying an algorithm

- 7. Proving an algorithm's correctness.

- 8. Analysing an algorithm.

- 9.Codinganalgorithm.

## 1. Understanding the problem:

- $\checkmark$  To design an algorithm, understand the problem completely by reading the problem's description carefully.

- $\checkmark$  Read the problem description carefully and clear the doubts.

- $\checkmark$  Specify exactly the range of inputs the algorithm need to handle.

- ✓ Once the problem is clearly understandable, then determine the overall goals but it should be in a precise manner.

- $\checkmark$  Then divide the problem into smaller problems until they become manageable size.

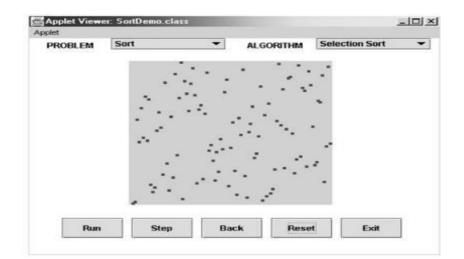

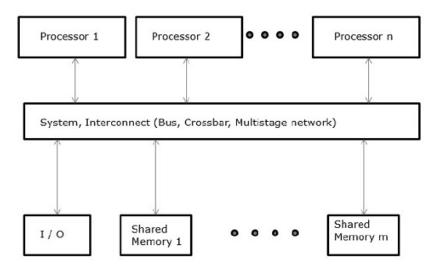

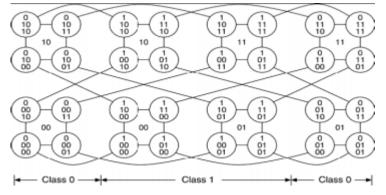

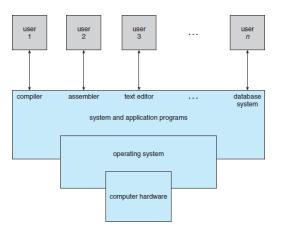

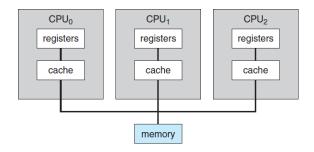

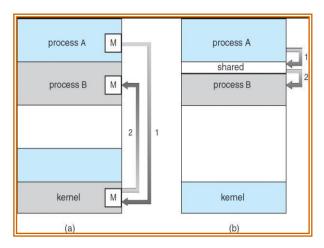

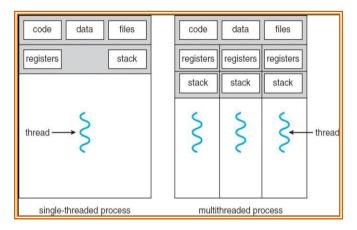

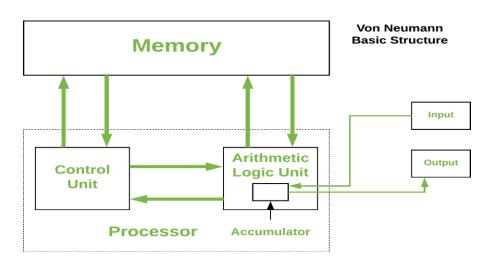

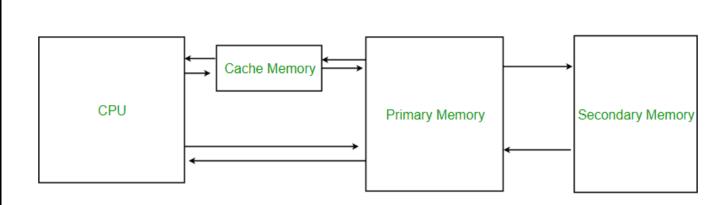

## 2. Ascertaining the capabilities of a computational device

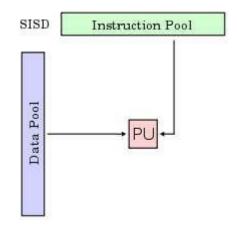

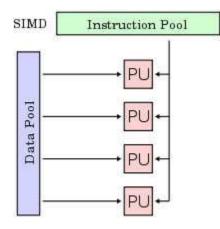

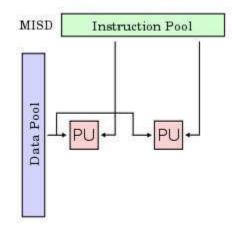

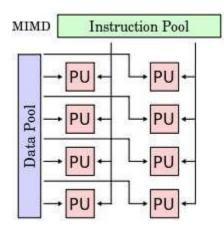

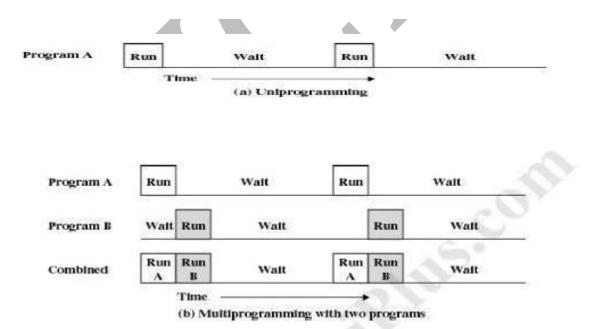

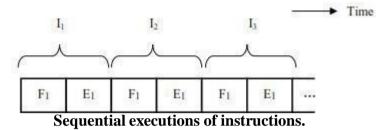

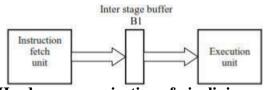

## **Sequential Algorithm:**

- $\checkmark$  Instructions are executed one after another, one operation at a time.

- ✓ This is implemented in RAM model.

## **Parallel Algorithm:**

✓ Instructions are executed in parallel or concurrently.

## 3. Choosing between exact and appropriate problem solving

- ✓ The next principal decision is to choose between solving the problem exactly or solving the problem approximately.

- ✓ The algorithm used to solve the problem exactly called **exact algorithm**.

- ✓ The algorithm used to solve the problem approximately is called **approximation algorithm.**

## Reason to choose approximate algorithm

- There are important problems that simply cannot be solved exactly such as

- Extracting square roots.

- Solving non linear equations.

- Evaluating definite integrals.

- $\checkmark$  Available algorithms for solving problem exactly can be unacceptably slow, because

of the problem's intrinsic complexity. Ex: Travelling salesman problem

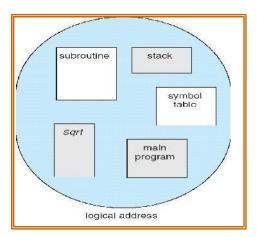

## 4. Deciding on appropriate data structures

Data structure is important for both design and analysis of algorithms.

## **Algorithm + Data Structures = Programs.**

In Object Oriented Programming, the data structure is important for both design and analysis of algorithms.

The variability in algorithm is due to the data structure in which the data of the program are stored such as

- 1. How the data are arranged in relation to each other.

- 2. Which data are kept in memory

- 3. Which data are kept in files and how the files are arranged.

- 4. Which data are calculated when needed?

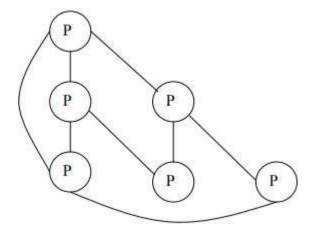

## **5. Algorithm Design Techniques**

An algorithm design techniques or strategy or paradigm is general approach to solving problems algorithmically that is applicable to a variety of problems from different areas of computing.

Uses

- $\checkmark$  They provide guidance for designing algorithms or new problems.

- $\checkmark$  They provide guidance to problem which has no known satisfied algorithms.

- $\checkmark$  Algorithm design technique is used to classify the algorithms based on the design idea.

- ✓ Algorithm design techniques can serve as a natural way to categorize and study the algorithms.

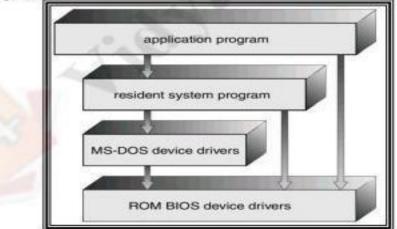

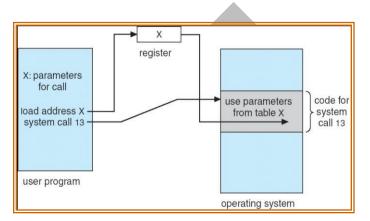

## 6. Methods of specifying an algorithm

There are two options, which are widely used to specify the algorithms.

They are

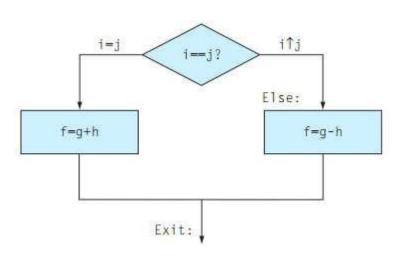

- Pseudo code

- Flowchart

## Pseudo code

- A pseudo code is a mixture of natural language and programming language constructs.

- A pseudo code is more precise than a natural language

- $\circ$  For simplicity, declaration of the variables is omitted.

- $\circ$  For, if and while statements are used to show the scope of the variables.

- $\circ$  "-(Arrow) used for the assignment operation.

- $\circ$   $\;$  "//" (two slashes) used for comments.

## Flow chart

- $\circ~$  It is a method of expressing an algorithm by a collection of connected geometric shapes containing description of the algorithms steps.

- $\circ$  It is very simple algorithm.

- This representation technique is inconvenient.

## 7. Proving an Algorithm's correctness

Once an algorithm has been specified, then its correctness must be proved.

- ✓ An algorithm must yield a required result for every legitimate input in a finite amount of time.

- ✓ A mathematical induction is a common technique used to prove the correctness of the algorithm.

- $\checkmark$  In mathematical induction, an algorithm's iterations provide a natural sequence of steps needed for proofs.

- $\checkmark$  If the algorithm is found incorrect, need to redesign it or reconsider other decisions.

## 8. Analysing an algorithm

$\checkmark$  Efficiency of an algorithm is determined by measuring the time, space and amount of

resources, it uses for executing the program.

- ✓ The efficiency of the algorithm is determined with respect to central processing units time and internal memory.

- $\checkmark$  There are two types of algorithm efficiency.

They are

- Time efficiency (or) Time Complexity

- Space efficiency (or) Space Complexity

## **Time Efficiency / Time Complexity**

- $\checkmark$  Time efficiency indicates how fast the algorithm runs.

- $\checkmark$  The time taken by a program to complete its task depends on the number of steps in an algorithm.

- $\checkmark$  The time required by a program to complete its task will not always be the same.

- $\checkmark$  It depends on the type of problem to be solved.

It can be of two types.

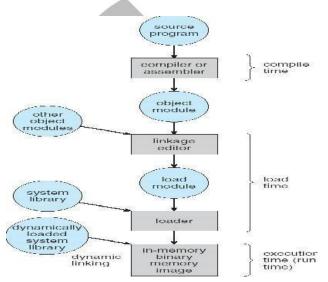

- Compilation Time

- Run Time (or) Execution Time

- $\checkmark$  The time (T) taken by an algorithm is the sum of the compile time and execution time.

## **Compilation Time**

- $\checkmark$  The amount of time taken by the compiler to compile an algorithm is known as compilation time.

- ✓ During compilation time, it does not calculate the executable statements, it calculates only the declaration statements and check for any syntax and semantic errors.

- $\checkmark$  The different compilers can take different times to compile the same program.

## **Execution Time**

- $\checkmark$  The execution time depends on the size of the algorithm.

- $\checkmark$  If the number of instructions in an algorithm is large then the run time is also large.

- $\checkmark$  If the number of instructions in an algorithm is small then the time need to execute the program is small.

- ✓ The execution time is calculated for executable statements and not for the declaration statements.

- $\checkmark$  The complexity is normally expressed as an order of magnitude.

- ✓ Example: O ( $n^{2}$ )

- ✓ The time complexity of a given algorithm is defined as computation of function f() as a total number of statements that are executed for computing the value f(n).

- $\checkmark$  The time complexity is a function which depends on the value of n.

The time complexity can be classified as 3 types. They are

- 1. Worst Case analysis

- 2. Average Case analysis

- 3. Best Case analysis

#### Worst Case Analysis

- ✓ The worst case complexity for a given size corresponds to the maximum complexity encountered among all problem of the same size.

- ✓ Worst case complexity takes a longer time to produce a desired result.

This can be represented by a function f(n).

$f(n) = n^2 \text{ or } n \log n$

#### Average Case Analysis

- ✓ The average case analysis is also known as the expected complexity which gives measure of the behaviour of an algorithm averaged over all possible problem of the same size.

- ✓ Average case is the average time taken by an algorithm for producing a desired output.

#### Best Case Analysis

$\checkmark$  Best case is a shortest time taken by an algorithm to produce the desired result.

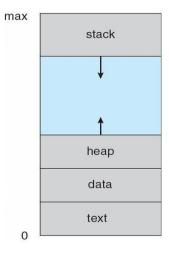

## **Space Complexity**

- $\checkmark$  Space efficiency indicates how much extra memory the algorithm needs.

- $\checkmark$  The amount of storage space taken by the algorithm depends on the type of the problem to be solved.

- $\checkmark$  The space can be calculated as,

- $\checkmark$  A fixed amount of memory occupied by the space for the program code is space occupied by the variable used in the program.

- $\checkmark$  A variable amount of memory occupied by the component variable dependent on the problem is being solved.

- $\checkmark$  This space is more or less depending upon whether the program uses iterative or recursive procedures.

There are three different space considered for determining the amount of memory used by the algorithm.

They are

- Instruction Space

- o Data Space

- Environment Space

#### **Instruction Space**

- ✓ When the program gets compiled, then the space needed to store the compiled instruction in the memory is called instruction space.

- $\checkmark$  The instruction space independent of the size of the problem

## Data Space

- $\checkmark$  The memory space used to hold the variables of data elements are called data space.

- $\checkmark$  The data space is related to the size of the Problem

## **Environment Space**

- $\checkmark$  It is the space in memory used only on the execution time for each Function call.

- $\checkmark$  It maintains runtime stack in that it holds returning address of the previous functions.

- $\checkmark$  Every function on the stack has return value and a pointer on it.

## **Characteristics of an algorithms**

- Simplicity

- o Generality

#### Simplicity

- $\circ$  Simpler algorithms are easier to understand.

- Simpler algorithms are easier to program.

- The resulting programs contains only few bugs.

- $\circ\;$  Simpler algorithms are more efficient compared to the complicated alternatives.

## Generality

- The characteristic of an algorithm generality has two issues.

- They are

- Generality' of the problem the algorithm solves.

- Range of inputs it accepts.

## 9. Coding an Algorithm

- ✓ Implementing an algorithm correctly is necessary but not sufficient to diminish the algorithm's power by an inefficient implementation.

- ✓ The standard tricks such as computing a loop's invariant (an expression that does not change its value) outside the loop, collecting common sub expressions, replacing expensive operations by cheaper ones and so on should be known to the programmers such factors can speed up a program only by a constant factor, where as a better algorithm can make a difference in running time by orders of magnitude.

- $\checkmark$  Once an algorithm has been selected, a 10-50% speed up may be worth an effort.

- ✓ An algorithm's optimality is not about the efficiency of an algorithm but about the complexity of the problem it solves.

## **3.** Explain the important problem types.

Some of the most important problem types are

- 1. Sorting

- 2. Searching

- 3. String Matching (or) String processing

- 4. Graph Problems

- 5. Combinatorial problems

- 6. Geometric problems

- 7. Numerical Problems

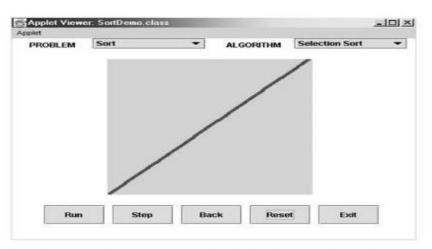

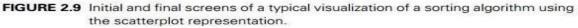

## 1. Sorting

- ✓ Sorting means arranging the elements in increasing order or in decreasing order.

- $\checkmark$  The sorting can be done on numbers , characters (alphabets), string or employees record.

- $\checkmark$  Many algorithms are used to perform the task of sorting.

- $\checkmark$  Sorting is the operation of arranging the records of a table according to the key value of the each record.

- ✓ A table of a file is an ordered sequence of records r[1], r[2].. r[n] each containing a key k[1], k[2]... k[n]. The table is sorted based on the key.

## **Properties of Sorting Algorithms**

The two properties of Sorting Algorithms are

- 1. Stable

- 2. In-place

## Stable:

- $\checkmark$  A sorting algorithm is called **stable**, if it preserves the relative order of any two equal elements in its input.

- ✓ In other words, if an input list contain two equal elements in positions i and j, where i<j, then in the sorted list they have to be in position i' and j' respectively, such that i' < j'</p>

## **In-place**

✓ An algorithm is said to be in-place if it does not require extra memory, except, possibly for a few memory units.

The important **criteria for the selection of a sorting** method for the given set of data items are as follows.

- 1. Programming time of the sorting algorithm.

- 2. Execution time of the program

- 3. Memory space needed for the programming environment

The **main objectives** involved in the design of sorting algorithms are

- 1. Minimum number of exchanges.

- 2. Large volume of data blocks movement.

## **Types of Sorting**

The two major classification of sorting methods are

- 1. Internal Sorting methods

- 2. External Sorting methods

## **Internal Sorting**

- ✓ The key principle of internal sorting is that all the data items to be sorted are retained in the main memory and random access memory.

- $\checkmark$  This memory space can be effectively used to sort the data items.

- $\checkmark$  The various internal sorting methods are

- 1. Bubble sort

- 2. Selection sort

- 3. Shell sort

- 4. Insertion sort

- 5. Quick sort

- 6. Heap sort

## **External Sorting**

- ✓ The idea behind the external sorting is to move data from secondary storage to mail memory in large blocks for ordering the data.

- $\checkmark$  The most commonly used external sorting method is merge sort.

## 2. Searching

- $\checkmark$  One of the important applications of array is searching

- ✓ Searching is an activity by which we can find out the desired element from the list. The element which is to be searched is called **search key**

- ✓ There are many searching algorithm such as sequential search , Fibonacci search and more. Searching in dynamic set of elements

- $\checkmark$  There may be of elements in which repeated addition or deletion of elements occur.

- $\checkmark$  In such a situation searching an element is difficult.

- ✓ To handle such lists supporting data structures and algorithms are needed to make the list balanced (organized)

## 3. String processing

A string is a collection of characters from an alphabet.

- Different type of strings are

- Text string

- Bit string

Text String It is a collection of letters, numbers and special characters.

- **Bit String** It is collection of zeros and ones.

- Operations performed on a string are

- 1. Reading and writing strings

- 2. String concatenation

- 3. Finding string length

- 4. String copy

- 5. String comparison

- 6. Substring operations

- 7. Insertions into a string

- 8. Deletions from a string

- 9. Pattern matching

## Pattern Matching or String matching

The process of searching for an occurrence of word in a text is called Pattern matching. Some of the algorithms used for pattern matching are

- 1. Simple pattern matching algorithm

- 2. Pattern matching using Morris Pratt algorithm

- 3. Pattern matching using Knuth-Morris-Pratt algorithm

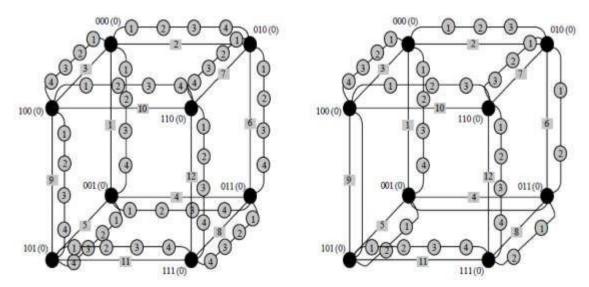

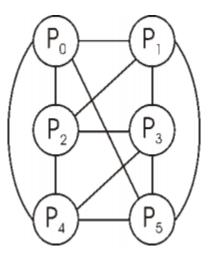

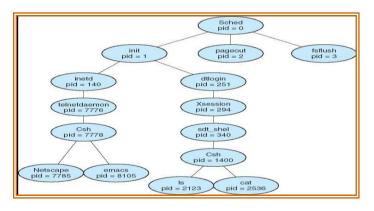

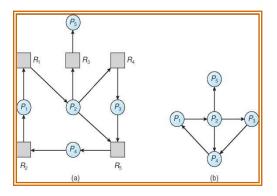

## 4. Graph Problems

- $\checkmark$  Graph is a collection of vertices and edges.

- ✓ Formally, a graph  $G=\{V, E\}$  is defined by a pair of two sets.

- $\checkmark$  A finite set V of items called Vertices and a set E of pairs of these items called edges.

- ✓ If the pairs of vertices are ordered, then G is called a directed graph because every edge is directed.

- ✓ In a directed graph the direction between two nodes are not same G(V,W)!=G(W,V)

- $\checkmark$  If the pair of the vertices are unordered then G is called an undirected graph.

- $\checkmark$  In undirected graph, the edges has no specific direction.

- ✓ The graph problems involve graph traversal algorithms, shortest path algorithm and topological sorting and so on. Some graph problems are very hard to solve.

- $\checkmark$  For example travelling salesman problem, graph colouring problems

## **5.** Combinatorial Problems

- $\checkmark$  The travelling salesman problem and the graph colouring problems are examples of combinatorial problems.

- ✓ A combinatorial object such as a permutation a combination or a subset that satisfies certain constraints and has some desired property such as maximizes a value or minimizes a cost should be find.

- ✓ Combinatorial problems are the **most difficult problems**.

## The reason is,

- 1. As problem size grows the combinatorial objects grow rapidly and reach to huge value. size.

- 2. There is no algorithms available which can solve these problems in finite amount of time

- 3. Many of these problems fall in the category of unsolvable problem.

- Some combinatorial problems can be solved by efficient algorithms.

## 6. Geometric Problems

- ✓ Geometric algorithms deal with geometric objects such as points ,lines and polygons.

- ✓ The procedure for solving a variety of geometric problems includes the problems of constructing simple geometric shapes such as triangles, circles and so on.

The two classic problems of computational geometry are the

- 2. Closest pair problem

- 3. Convex hull problem

- ✓ The closest pair problem is self explanatory. Given n points in the plane, find the closest pair among them.

- ✓ The convex hull problem is used to find the smallest convex polygon that would include all the points of a given set.

- ✓ The geometric problems are solved mainly in applications to computer graphics or in robotics

## 6.Numerical problems

- ✓ Numerical problems are problems that involve mathematical objects of continuous nature such as solving equations and systems of equations computing definite integrals evaluating functions and so on.

- $\checkmark$  Most of the mathematical problems can be solved approximate algorithms.

- ✓ These algorithms require manipulating of the real numbers; hence we may get wrong output many times.

## 3.Explain the fundamentals of the analysis framework. Or explain time-space trade off of the algorithm designed. April/May 2019

- Efficiency of an algorithm can be in terms of time or space.

- This systematic approach is modelled by a frame work called as analysis frame work.

## **Analysis framework**

- $\circ~$  The efficiency of an algorithm can be decided by measuring the performance of an algorithm.

- The performance of an algorithm is computed by two factors

- amount of time required by an algorithm to execute

- amount of storage required by an algorithm

## **Overview**

- Space complexity

- Time complexity

- Measuring an Input's size

- Measuring Running Time

- Orders of Growth

## Space complexity

• The space complexity can be defined as amount of memory required by an algorithm to run.

- To compute the space complexity we use two factors: constant and instance characteristics.

- The space requirement S(p) can be given as S(p) = C + S(p)

Where C is a constant i.e. fixed part and it denotes the space of inputs and outputs.

## Time complexity

- The time complexity of an algorithm is the amount of computer time required by an algorithm to run to completion.

- For instance in multiuser system, executing time depends on many factors such as

- System load

- Number of other programs running

- Instruction set used

- Speed underlying hardware

- The time complexity is therefore given in term of frequency count

- Frequency count is a count denoting number of times of execution of statement

## Example

For (i=0; i<n; i++) { sum = sum + a[i]; }

| Statement                                                                                                                                                                                                                                                              | Frequency count                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| i=0                                                                                                                                                                                                                                                                    | 1                                                                                                                                                                                                                                 |

| i <n< td=""><td>This statement executes for <math>(n+1)</math> times. When<br/>conditions is true i.e. when i<n execution<br="" is="" the="" true,="">happens to be n times, and the statement execute once<br/>more when i<n false<="" is="" td=""></n></n></td></n<> | This statement executes for $(n+1)$ times. When<br>conditions is true i.e. when i <n execution<br="" is="" the="" true,="">happens to be n times, and the statement execute once<br/>more when i<n false<="" is="" td=""></n></n> |

| i++                                                                                                                                                                                                                                                                    | n times                                                                                                                                                                                                                           |

| sum = sum + a[i]                                                                                                                                                                                                                                                       | n times                                                                                                                                                                                                                           |

| Total                                                                                                                                                                                                                                                                  | 3n + 2                                                                                                                                                                                                                            |

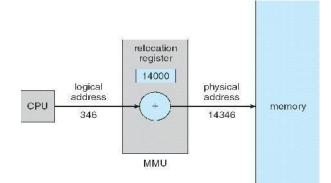

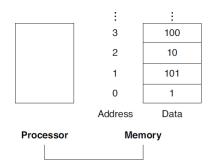

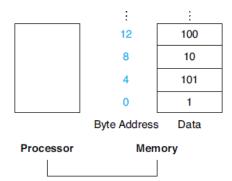

## Measuring an Input's size

- All algorithms run longer on larger inputs.

- Ex: Sorting larger arrays, multiply larger matrices etc.

- Investigates an algorithm efficiency as a function of some parameter n indicating the algorithm input size.

- Example:

- $\circ$  In problem of evaluating a polynomial  $p(x) = a_n x^{n} + ... + a_0$  of degree n, the parameter will be the polynomial's degree or the number of its coefficients which is larger by one than its degree.

- In spell checking algorithm,

- If algorithm examines the individual character of its input, then the size of the input is the no. of characters.

- If the algorithm processes the word, the size of the input is the no. of words.

## Measuring Running Time

- Some units of time measurement such as a second, a millisecond and so on can be used to measure the running time of a program implementing the algorithm.

- Drawbacks

- l. Dependence on the speed of a particular computer

- 2. Dependence on the quality of a program implementing the algorithm.

- 3. The compiler used in generating the machine code.

- 4. The difficulty of clocking the actual running time of the program

- Since we are in need to measure an algorithm's efficiency, we should have a metric that does not depend on these factors.

- One possible approach is to count the number of times of the algorithm's operations is executed. But this approach is difficult and unnecessary.

- The main objective is to identify the most important operation of the algorithm, called the **Basic Operation** the operation contributing the most to the total running time, and compute the number of times the basic operation is executed.

- It is not so difficult to identify the basic operation of an algorithm: it is usually the most time consuming operation in the algorithm's innermost loop.

## Example

• Most sorting algorithms work by comparing the elements (keys) of a list being sorted with each other. For such algorithms the basic operation is a Key Comparison.

| Problem statement                                         | Input Size                               | Basic operation                                       |  |  |

|-----------------------------------------------------------|------------------------------------------|-------------------------------------------------------|--|--|

| Searching a key<br>element from the<br>list of n elements | List of n elements                       | Comparison of key with every element of list          |  |  |

| Performing matrix multiplication                          | The two matrixes with order $n \times n$ | Actual multiplication of the elements in the matrices |  |  |

| Computing GCD of two numbers                              | Two numbers                              | Division                                              |  |  |

The formula to compute the execution time using basic operation is

$$\mathbf{T}(\mathbf{n}) \approx \mathbf{C}_{\mathrm{op}} \mathbf{C}(\mathbf{n})$$

Where T(n) – running time

- C(n) no. of times this operation is executed.

- Cop execution time of algorithms basic operation.

## **Orders of Growth**

• Measuring the performance of an algorithm in relation with the input size n is called order of growth.

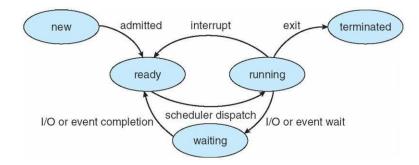

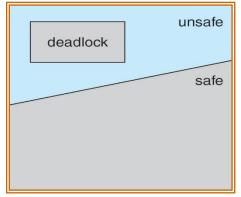

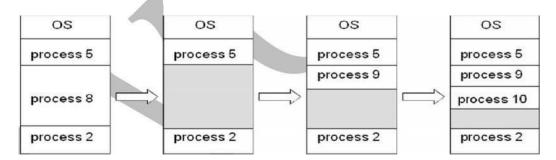

## Worst Case, Best Case and Average Case efficiencies

- It is reasonable to measure an algorithm's efficiency as a function of a parameter indicating the size of the algorithm's input.

- But for many algorithms the running time depends not only on an input size but also on the specifics of a particular input.

## Example: Sequential Search or Linear Search AU: Dec -11, Marks 10

ALGORITHM SequentialSearch(A[0..n - 1], K) //Searches for a given value in a given array by sequential search //Input: An array A[0..n - 1] and a search key K//Output: The index of the first element in A that matches K// or -1 if there are no matching elements  $i \leftarrow 0$ while i < n and A[i] = K do  $i \leftarrow i + 1$ if i < n return ielse return -1

• This algorithm searches for a given item using some search key K in a list of 'n' elements by checking successive elements of the list until a match with the search key

is found or the list is exhausted.

• The algorithm makes the largest number of key comparisons among all possible inputs of size n:C<sub>worst</sub>(n)=n

## Worst case efficiency

- The worst case efficiency of an algorithm is its efficiency for the worst case input of size n, which is an input (or inputs) of size n. For which the algorithm runs the longest among all possible of that size.

- The way to determine the worst case efficiency of an algorithm is that:

- Analyse the algorithm to see what Kind of inputs yield the largest value of the basic operations count C(n) among all possible inputs of size n and then compute is w value  $C_{worst} = (n)$ .

#### **Best case efficiency**

- The best case efficiency of an algorithm is its efficiency for the best case input of size n, which is an input (or inputs) of. size n for which the algorithm runs the fastest among all possible inputs of that size.

- The way to determine the best case efficiency of an algorithm is as follows.

- First, determine the kind of inputs of size n.

- $\circ$  Then ascertain the value of C(n) on these inputs.

- **Example:** For sequential search, the best case inputs will be lists of size 'n' with their first elements equal to a search key:  $C_{best}(n) = 1$ .

## Average case efficiency

- It yields the necessary information about an algorithm's behaviour on a "typical" or "random" input.

- To determine the algorithm's average case efficiency some assumptions about possible inputs of size 'n'.

- The average number of key comparisons  $C_{avg}(n)$  can be computed as follows:

- In case of a successful search the probability of the first match occurring in the position of the list is p/n for every i. and the number of comparisons made by the algorithm in such a situation is obviously 'i'.

- $\circ$  In case of an unsuccessful search, the number of comparisons is 'n' with the probability of such a search being (1-p). Therefore,

$$C_{avg}(n) = [1.n+2.n+....i.n+1]+n.(1-p)$$

$$= n[1+2+3+...+i+...+n]+n(1-p)$$

$$= \frac{p n(n+1)}{n 2} + n(1-p)$$

There may be n elements at which chances of 'not getting element' are possible. Hence n . (1-p)

$$C_{avg}(n) = \frac{p(n+1)}{2n} + n(1-p)$$

#### Example:

- If p = 1 (i.e.) if the search is successful, then the average number of key comparisons made by sequential search is (n+1)/2.

- $\circ$  If p = 0 (i.e.) if the search is unsuccessful, then the average number of key comparisons will be 'n' because the algorithm will inspect all n elements on all such inputs.

- 4. Explain the Asymptotic Notations and its properties? Or explain briefly Big oh notation , Omega notation and Theta notation give an example (Apr/May-2017) or what are the Rules of Manipulate Big-Oh Expression and about the typical growth rates of

#### algorithms? Nov/Dec 2017 Nov/Dec 2018

## Define Big O notation, Big Omega and Big Theta Notation. Depict the same graphically and explain. May/June 2018, Nov/Dec 2019

## Explain the importance of asymptotic analysis for running time of an algorithm with an example. (April/May 2021)

Asymptotic notations are mathematical tools to represent time complexity of algorithms for measuring their efficiency. Types :

- Big Oh notation 'O'

- Omega notation ' $\Omega$ '

- $\circ$  Theta notation ' $\Theta$ '

- Little Oh notation 'o '

## **Big Oh notation (O)**

- The big oh notation is denoted by **'O'**.

- It is a method of representing the **upper bound of algorithm's running time.**

- Using big oh notation we can give **longest amount of time taken** by the algorithm to complete.

#### Definition

A function t(n) is said to be in O(g(n)) ( $t(n) \in O(g(n))$ ), if t(n) is bounded above by constant multiple of g(n) for all values of n, and if there exist a positive constant c and non negative integer n0 such that

O Big-oh notation:  $t(n) \in O(g(n))$ .

#### Example 1:

Consider function t(n) = 2n + 2 and  $g(n) = n^2$ . Then we have to find some constant c, so that  $f(n) \le c^*g(n)$ .

As t(n) = 2n + 2 and  $g(n) = n^2$ . Then we find c for n=1 then t(n) = 2n + 2= 2(1) + 2t(n) = 4 $g(n) = n^2$ And  $= (1)^{2}$ g(n) = 1t(n) > g(n)i.e if n = 2 then, t(n) = 2n + 2= 2(2) + 2t(n) = 6And  $g(n) = n^2$  $= (2)^{2}$ g(n) = 4t(n) > g(n)i.e if n = 3 then. t(n) = 2n + 2

= 2(3) + 2 t(n) = 8And  $g(n) = n^{2}$   $= (3)^{2}$  g(n) = 9i.e t(n) < g(n) is true.Hence we can conclude that for n> 2, we obtain t(n) < g(n)Thus always upper bound of existing time is obtained by big oh notation.

#### **Omega Notation** $(\Omega)$

Omega notation is denoted by ' $\Omega$ '.

This notation is used is to represent the **lower bound of algorithm's** running time. Using omega notation we can denote **shortest amount of time taken** by algorithm.

#### Definition

A function t(n) is said to be in  $\Omega(g(n))$  ( $t(n) \in \Omega(g(n))$ ), if t(n) is bounded below by constant multiple of g(n) for all values of n, and if there exist a positive constant c and non negative integer n0 such that

Example 1: 0 Consider  $t(n)=2n^2+5$  and g(n)=7nif n = 0Then  $t(n) = 2 (0)^2 + 5$ = 5 g(n) = 7(0)= 0 i.e t(n) > g(n)if n = 1But  $t(n) = 2(1)^2 + 5$ = 7 g(n) = 7(1)= 7 i.e t(n) = g(n)But if n = 2 $t(n) = 2 (2)^2 + 5$ = 9 g(n) = 7(2)= 12i.e t(n) < g(n)But if n = 3 $t(n) = 2 (3)^2 + 5$ = 18 + 5= 23g(n) = 7(3)= 21i.e t(n) > g(n)Thus for n>3 we get t(n) > c \* g(n). It can be represented as

32

#### **Theta Notation** ( $\Theta$ )

$2n^2 + 5 \in \Omega(n)$

The theta notation is denoted by  $\Theta$ . By this method the **running time is between upper bound and lower bound.**

#### Definition

A function t(n) is said to be in  $\Theta(g(n))$  ( $t(n) \in \Theta(g(n))$ ), if t(n) is bounded both above and below by constant multiple of g(n) for all values of n, and if there exist a positive constant c1 and c2 and non negative integer n0 such that

for all n >

#### Example 1:

If t(n) = 2n + 8 and g(n) = 7n, 5nWhere n > 2 $C2^*g(n) \le t(n) \le c1^*g(n)$ for all  $n \ge 1$  $\Theta(g(n)) = O(g(n)) \Omega(g(n))$  $(t(n) \in \Theta(g(n)))$ Similarly t(n) = 2n + 8g(n) = 7ng(n) = 5ni.e 5n < 2n + 8 < 7n for  $n \ge 2$ Here  $c_2 = 5$  and  $c_1 = 7$  with  $n_0 = 2$ Little oh notation(o) The function t(n) = o(g(n)), if O(g(n)) and  $t(n) <> \Omega(g(n))$ Example t(n) = 3n+2Where n > 0,  $3n + 2 \le 5 n^2$ By definition of Big Oh  $\mathbf{t}(\mathbf{n}) = \mathbf{C}\mathbf{g}(\mathbf{n})$  $C = 5; g(n) = n^2$ But  $t(n) = 3n+2 <> \Omega(n^2)$ Therefore  $t(n) = 3n+2 = o(n^2)$

#### Useful property involving the Asymptotic notation:

The following property is useful in analyzing algorithms that comprise two consecutively executed parts.

#### Theorem

If  $t_1(n) \in O(g_1(n))$  and  $t_2(n) \in O(g_2(n))$  then,  $t_1(n) + t_2(n) \in (\max \{g_1(n), g_2(n)\})$

#### Proof

Since  $t_1(n) \in O(g_1(n))$ , there exist some constant  $C_1$  and some non negative integer  $n_1$  such that  $t_1(n) \leq C_1 (g_1(n))$  for all  $n \geq n_1$

Since

$t_2(n) \in O(g_2(n))$

$t_2(n) \leq C_2$  (g<sub>2</sub>(n)) for all  $n \geq n_2$

Let us denote,

$C_3 = \max \{C_1, C_2\}$  and

Consider  $n \ge max \{n_1, n_2\}$ , so that both the inequalities can be used. The addition of two inequalities becomes,

> $t_1(n)+t_2(n) \le C_1 (g_1(n))+C_2 (g_2(n))$  $\leq C_3 (g_1(n)) + C_3 (g_2(n))$  $\leq C_3 2 \max\{g_1(n), (g_2(n))\}$

Hence,

$t_1(n) + t_2(n) \in O(\max \{g_1(n), g_2(n)\}),$

with the constants C and  $n_0$  required by the definition being  $2C_3 = 2 \max (C_1, C_2)$  and max  $\{n_1, n_2\}$  respectively.

The property implies that the algorithms overall efficiency will be determined by the part with a larger order of growth.

(i.e.) its least efficient part is

$t_1(n) + t_2(n) \in O (max \{g_1(n), g_2(n)\})$  $t_1(n) \in O(g_1(n))$  $t_2(n) \in O(g_2(n))$

#### Using limits for comparing orders of growth

There are 3 principal cases,

|                               | 0, | Implies               | that    | (n) | has | a | smaller | order |

|-------------------------------|----|-----------------------|---------|-----|-----|---|---------|-------|

|                               |    | of growth than $g(n)$ |         |     |     | ( |         |       |

| $\lim_{n\to\infty} t(n)/g(n)$ | С, | Implies               | that    | (n) | has | a | same    | order |

| n→∞                           |    | of growth than g(n)   |         |     |     |   |         |       |